## DSP

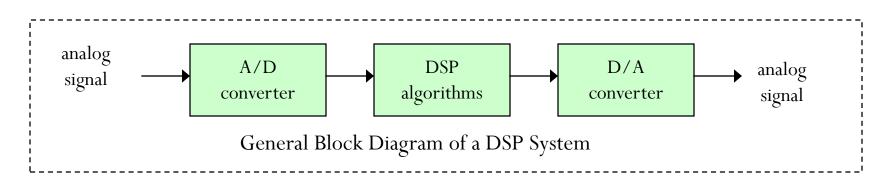

- Digital Signal Processing (DSP)

- Is the manipulation of digital signals in order to modify their characteristic or to extract useful information. Why digital and not analog?

- Digital signal allow programmability,

- Digital circuit allow for stable output than analog

- Microprocessors and computers have become so powerful

- only digitized signal can be processed by computers.

- Digital Signal Processor (DSP)

- DSP is a specialized microprocessor optimized for signal processing.

- General purpose microprocessors such as Pentium series microprocessors that are used in PC are not optimized for signal processing purposes.

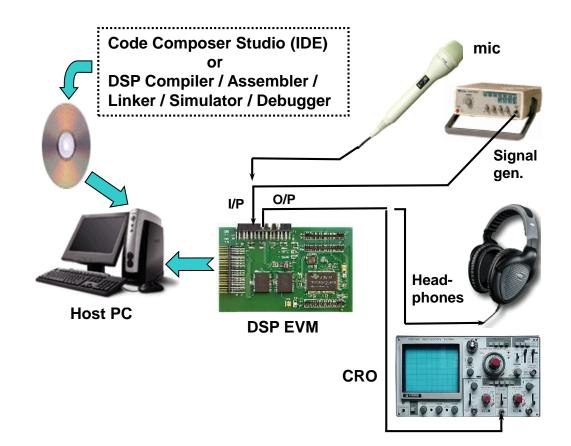

Hardware tools:

DSP (DSKs), evaluation modules (EVMs) and other DSP boards

→ For real-time DSP experiments, a DSK/EVM/Emu. is suitable along with a host system, which can be a typical PC.

Software tools:

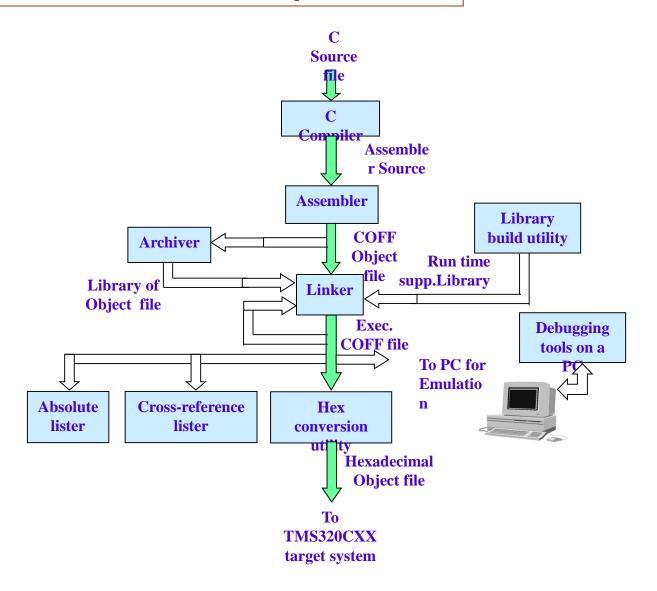

Assembly language tools, DSP simulator, C compiler and C source debugger.

Code Composer Studio (CCS) → IDE:

Simulates, C compiles and works with a DSK

### DSP Software Development flow

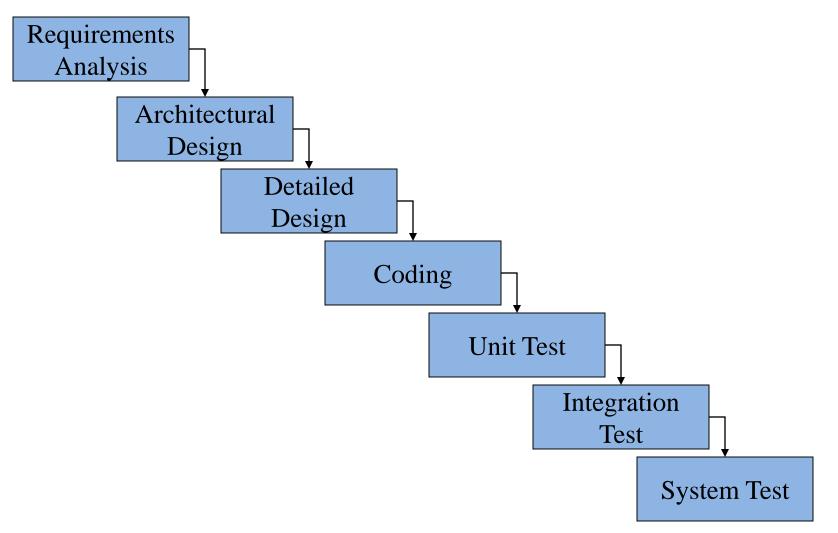

### Software Life Cycle - Waterfall Method

## Texas Instruments' TMS320 family

Video

## TMS320 DSP Families

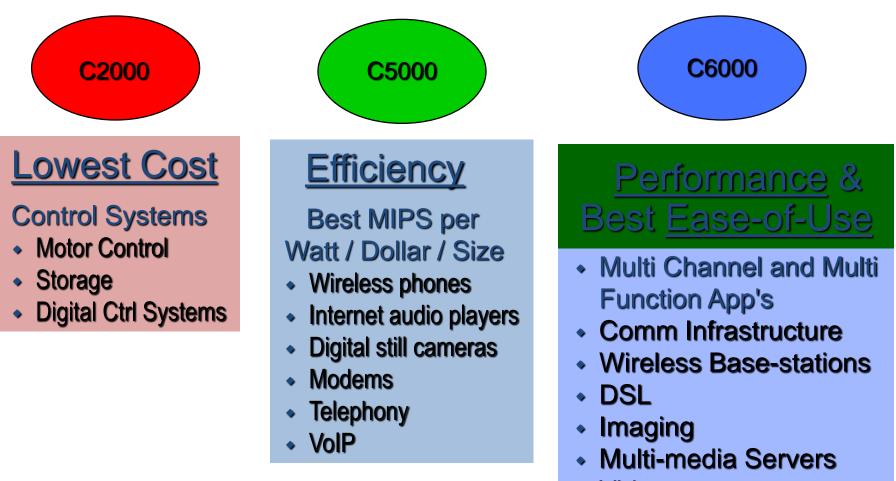

>50 Products ASP: \$3 - \$15 >100 Products ASP: \$5 - \$120

- World's most code-efficient DSP

- Advanced embedded control applications

- Leadership integration of analog and high-speed Flash memory

- C28x fully code compatible

- World's most powerefficient DSP

- World's most popular DSP

- Heart of handheld solutions in Internet era

- C55x fully code compatible `

### >30 Products ASP: \$10 - \$350

- World's highestperformance DSP

- Used in high-bandwidth comms and video equipment

- C64x fully code compatible

## Floating vs. Fixed point processors

- Applications which require:

- High precision.

- Wide dynamic range.

- High signal-to-noise ratio.

- Ease of use.

- Need a floating point processor.

- Drawback of floating point processors:

- Higher power consumption.

- Can be more expensive.

- Can be slower than fixed-point counterparts and larger in size.

## Floating vs. Fixed point processors

- It is the application that dictates which device and platform to use in order to achieve optimum performance at a low cost.

- For educational purposes, use the floating-point device (C6713) as it can support both fixed and floating point operations.

- Fixed point processors:

- TMS320c2X, TMS320c5X and TMS320c62X

- (Modulators, demodulators, carrier and clock recovery etc.,)

- Floating point processors:

- TMS320c3X and TMS320c67X

- (Speech processing, control systems, equalization etc.,)

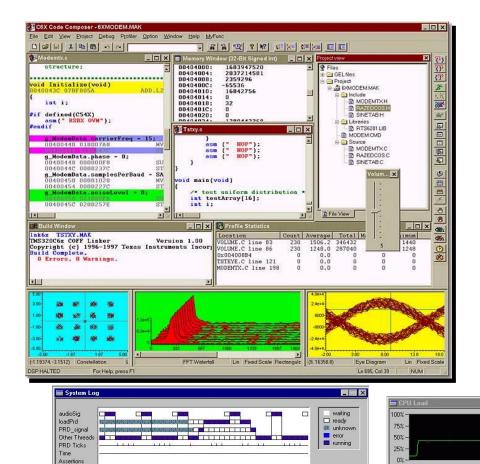

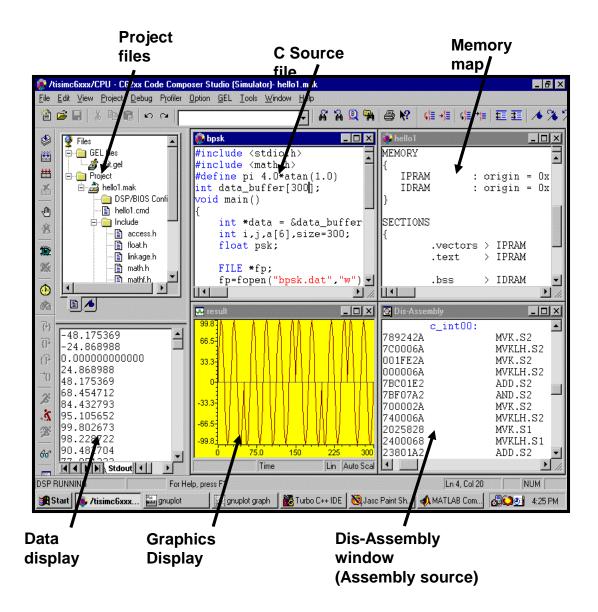

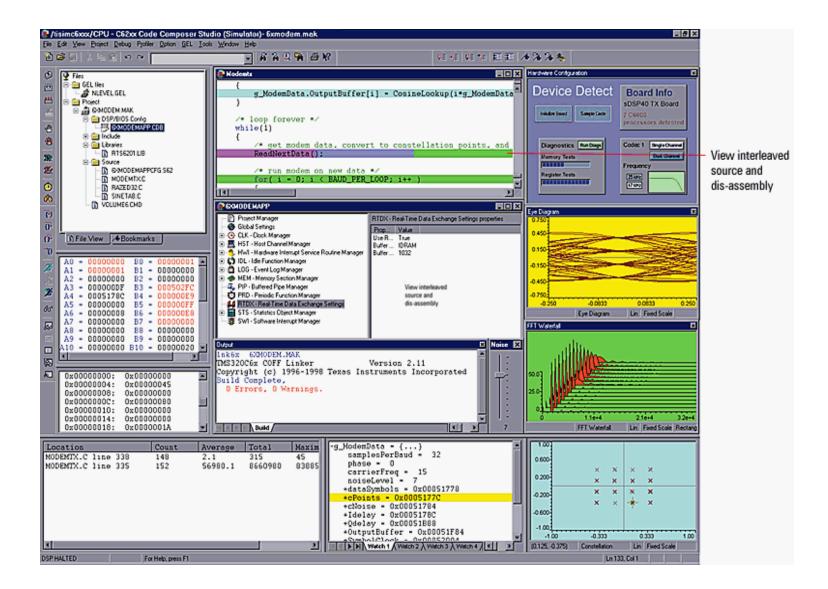

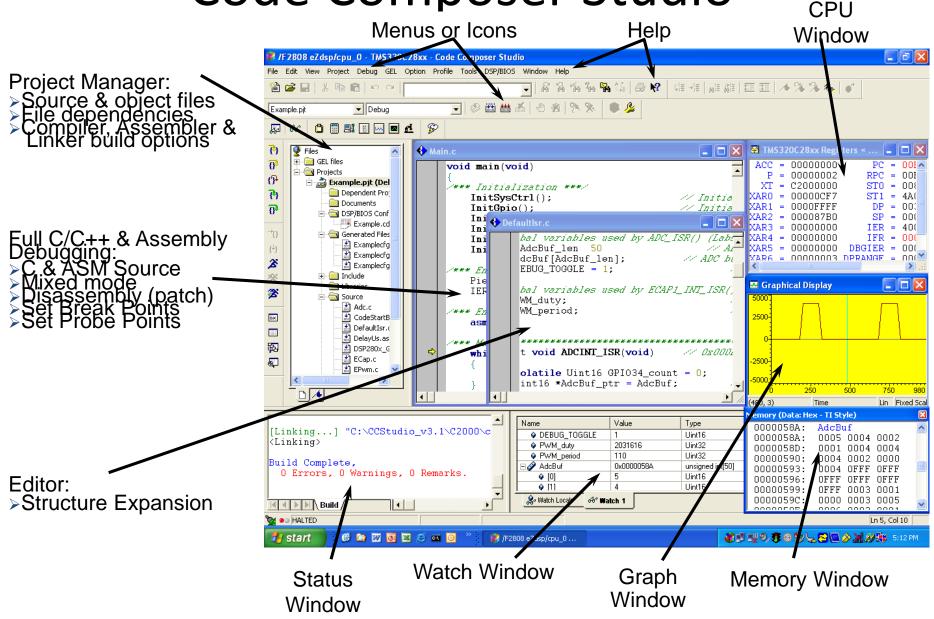

## Code Composer Studio

- 🗆 ×

Last: 8.53% ±0.1 Peak: 42.93%

40

10 15

20

25 30

- DSP industry's first comprehensive, open Integrated Development Environment (IDE)

- > Advanced visualization

- > Intuitive ease-to-use

- > Third-party plug-ins

- Visualization without stopping the processor

|            | Count | Max       | Average    |

|------------|-------|-----------|------------|

| loadPrd    | 5784  | 5 ticks   | 2.53 ticks |

| audioSig 🗍 | 23264 | 3458.0 us | 475.3 us   |

The CCS is an integrated suite of DSP software development tools

efficient 'C6000 C compiler, Assembly Optimizer with the Code Composer IDE, Advanced Data Visualization, standard open APIs, DSP/BIOS and Real-Time Data Exchange(RTDX)

- Optimizing C compiler → fully exploits the architecture's instructionlevel parallelism and orthogonal instruction set

- Assembly optimization

supports automatic scheduling, optimizing and separation of parallel tasks from linear assembly code

- Debugger → Conditional or hardware breakpoints are based on full Cexpressions, local variables or CPU register symbols.

- Real-Time Analysis → Using RTDX technology, DSP/BIOS provides a real-

## Code Composer Studio

# **Real-Time Processing**

- Real-time processing means:

- The processing of a particular sample must occur within a given time period or the system will not operate properly.

- Real-time DSP is inherently an *interrupt* driven process. The input samples should only be processed using interrupt service routines (ISR).

- Hard real-time system

- The system will fail if the processing is not done in a timely manner.

- Soft real-time system

- The system will tolerate some failures to meet real-time targets and still continue to operate, but with some degradation in performance.

- The performance demands and power constraints of real-time systems often mandate specialized hardware.

- That may include the digital signal processor (DSP), programmable logic devices, application specific integrated circuits (ASIC), and etc.

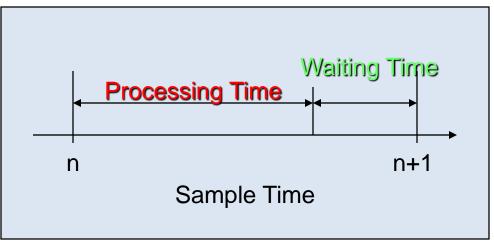

### Real-time processing

- We can say that we have a real-time application if:

- Waiting Time  $\geq 0$

- DSP processors have to perform tasks in real-time, so how do we define real-time?

- The definition of real-time depends on the application.

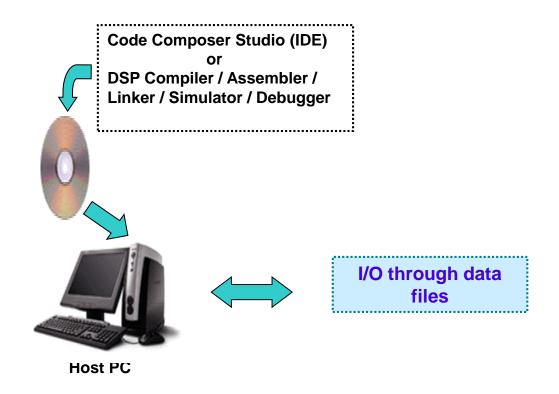

### A Setup for Non-real-time Experiment

Assembly language code and implementation flavor is present, but real-time experiments cannot be carried out using this setup.

### A Setup for Real-time Experiments

Assembly language code and implementation flavor is present. Real-time experiments can be carried out using this setup.

### Hardware vs. Microcode multiplication

- DSP processors are optimized to perform multiplication and addition operations.

- Multiplication and addition are done in hardware and in one cycle.

- Example: 4-bit multiply (unsigned).

| Hardware                  | Microcode             |                    |

|---------------------------|-----------------------|--------------------|

| 1011                      | 1011                  |                    |

| <u>x 1110</u><br>10011010 | <u>× 1110</u><br>0000 | Cuala 1            |

| 10011010                  | 1011.                 | Cycle 1<br>Cycle 2 |

|                           | 1011                  | Cycle 3            |

|                           | 1011                  | Cycle 4            |

|                           | 10011010              | Cycle 5            |

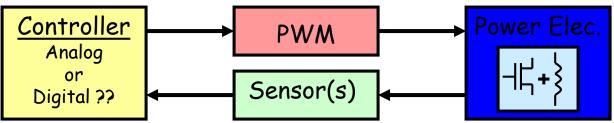

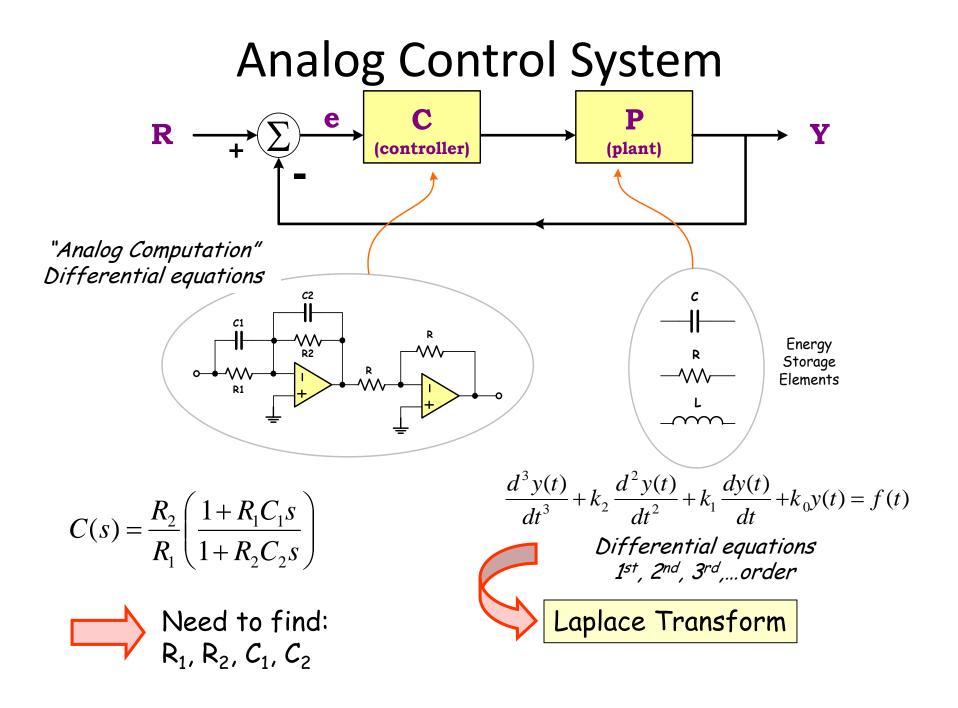

## Why Digital Control Techniques?

|   | Analog Controller                                                                                                                                                                                                         | Digital Controller                                                                                                                                                                                                                                                                                   |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + | <ul> <li>High bandwidth</li> <li>High resolution</li> <li>Easy to understand / use</li> <li>Historically lower cost</li> </ul>                                                                                            | <ul> <li>Insensitive to environment (temp, drift,)</li> <li>S/w programmable / flexible solution</li> <li>Precise / predictable behavior</li> <li>Advanced control possible (non-linear, multi-variable)</li> <li>Can perform multiple loops and "other" functions</li> </ul>                        |

|   | <ul> <li>Component drift and aging / unstable</li> <li>Component tolerances</li> <li>Hardwired / not flexible</li> <li>Limited to classical control theory only</li> <li>Large parts count for complex systems</li> </ul> | <ul> <li>Bandwidth limitations (sampling loop)</li> <li>PWM frequency and resolution limits</li> <li>Numerical problems (quantization, rounding,)</li> <li>AD / DA boundary (resolution, speed, cost)</li> <li>CPU performance limitations</li> <li>Bias supplies, interface requirements</li> </ul> |

### **Benefits of Digital Control**

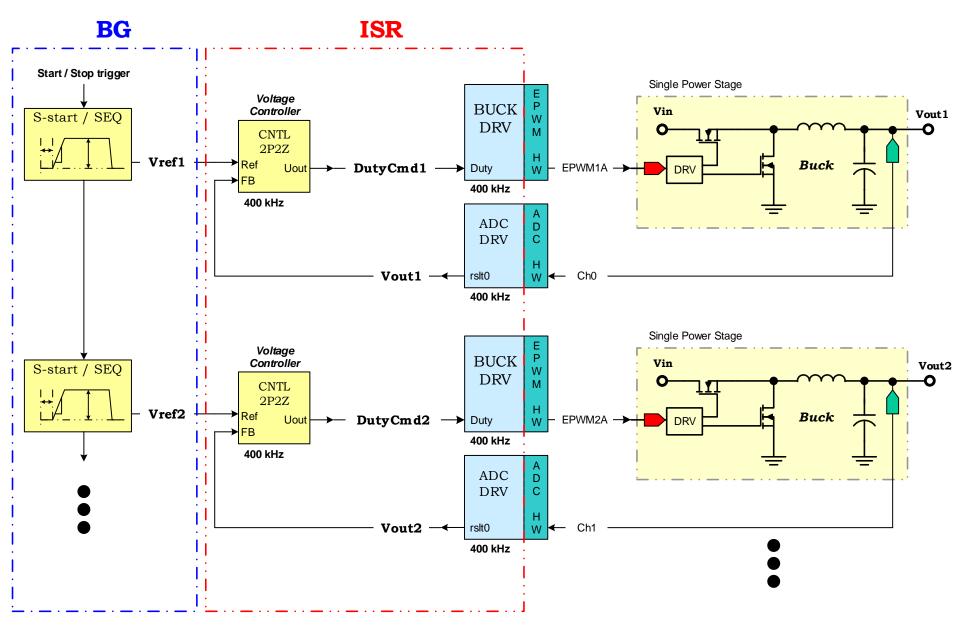

Digital controller enables multi-threaded applications

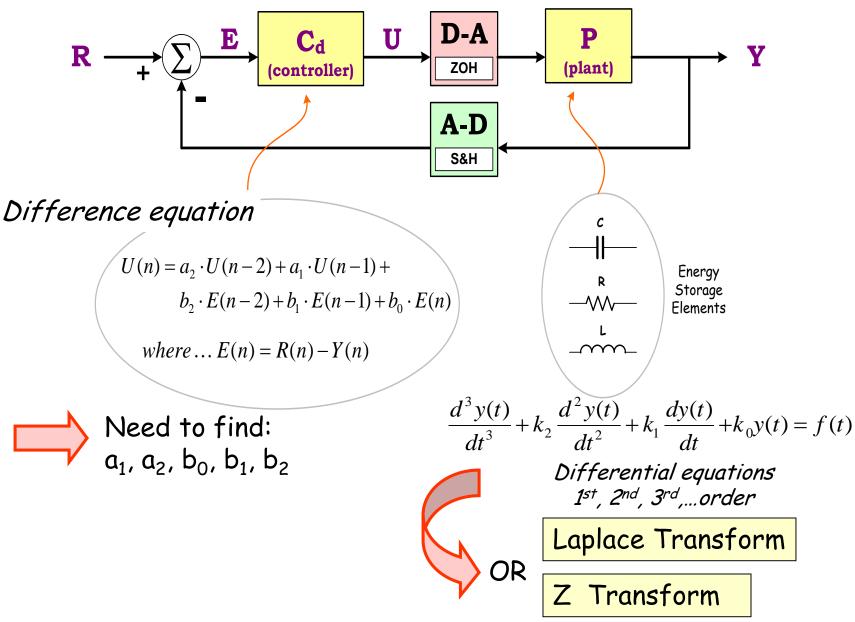

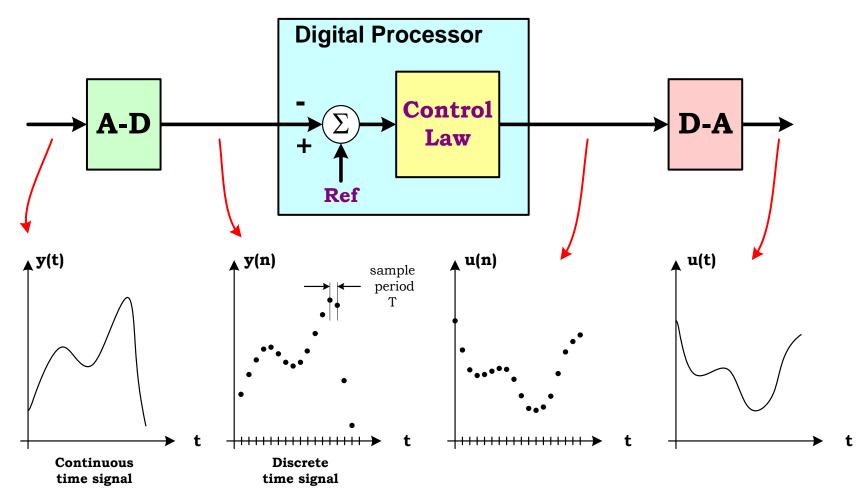

### **Time Sampled Systems**

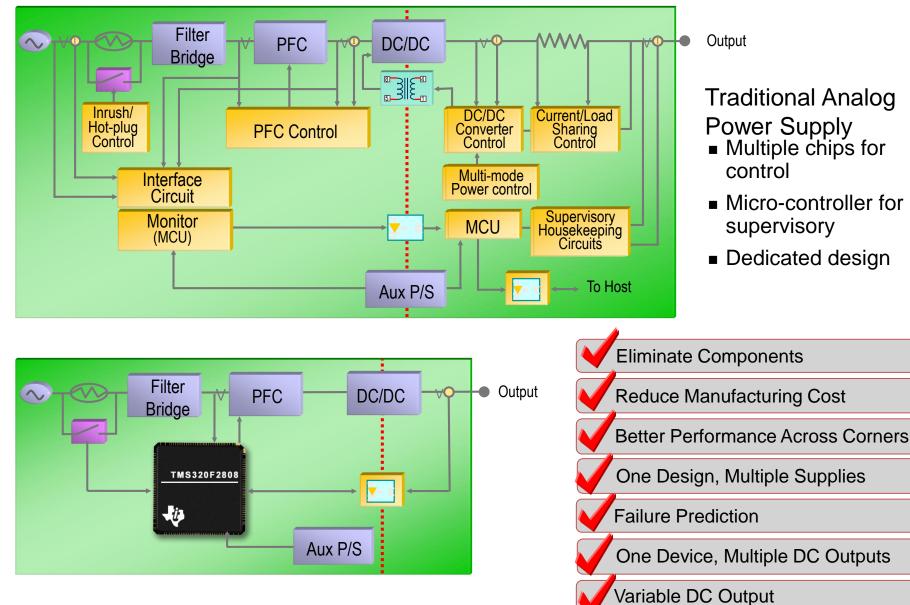

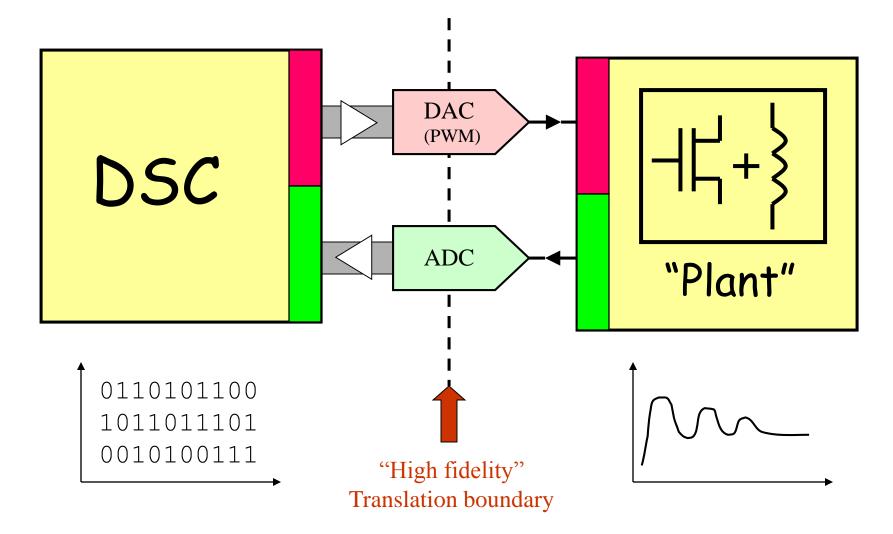

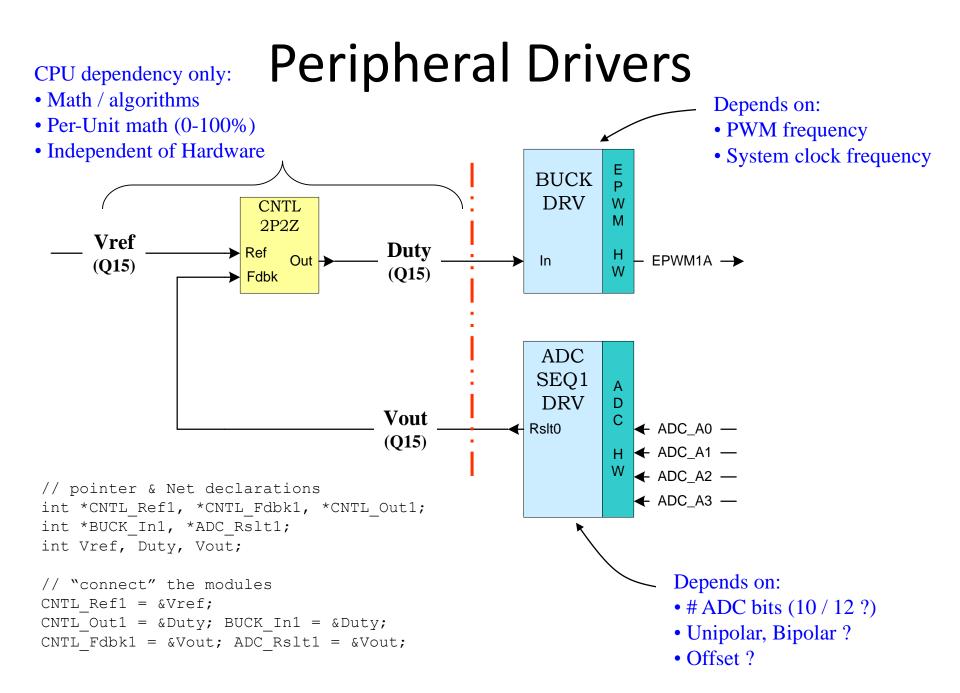

## **Digitally Controlled Power Supply**

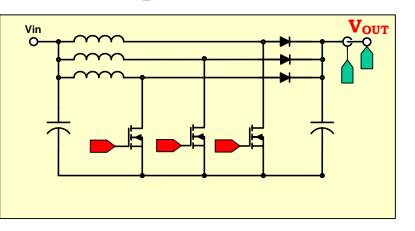

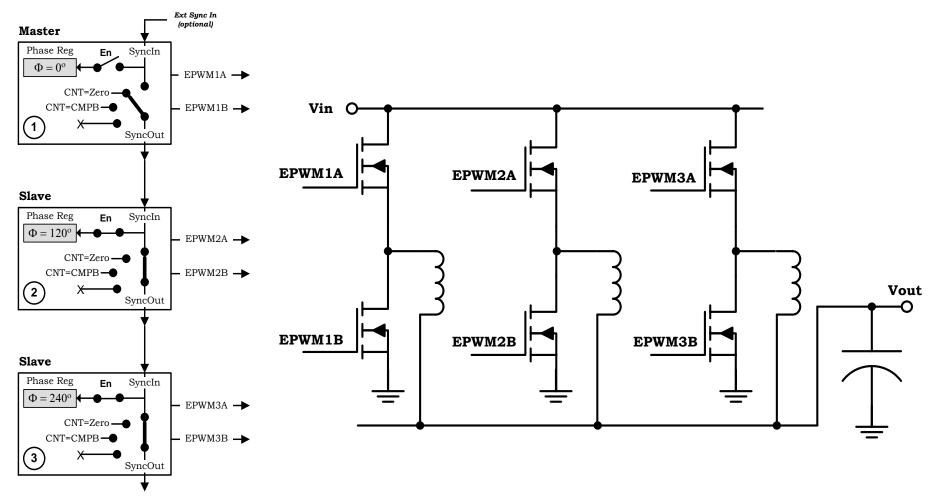

### System Mapping PFC - 3ph Interleaved

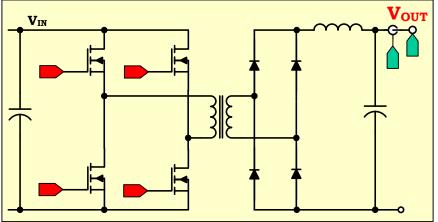

#### **Phase-Shifted Full Bridge**

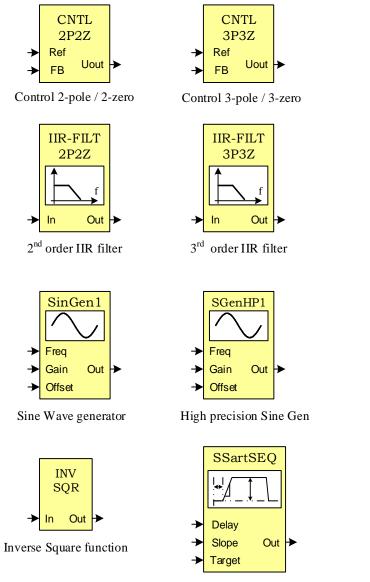

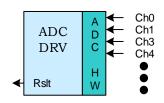

### Software Library Approach

Soft Start and Sequencing

Analog-Digital Converter driver

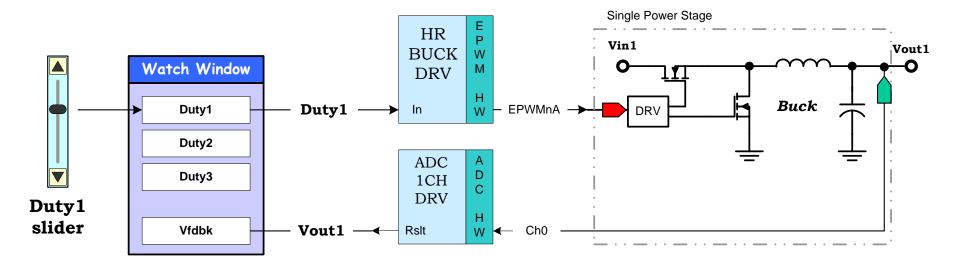

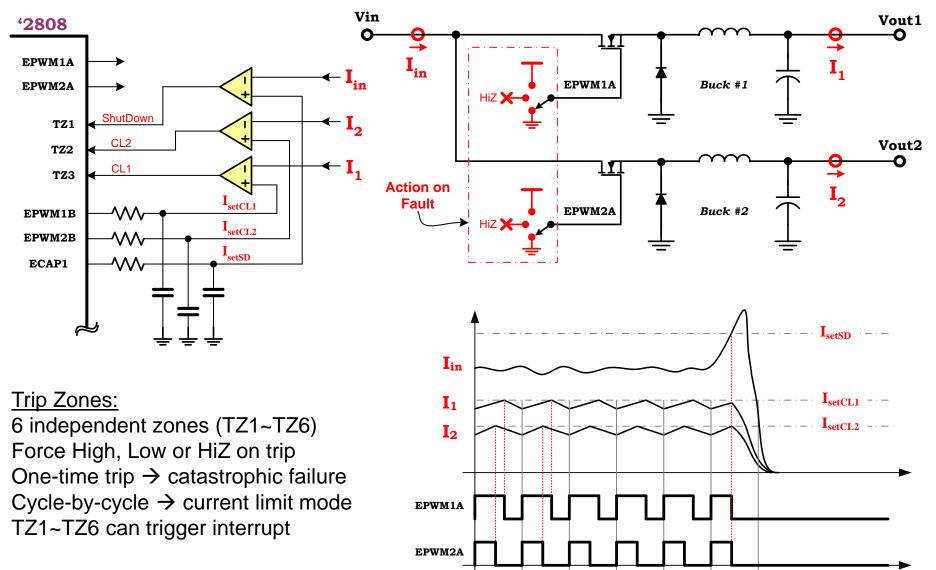

### **Dual Buck Example**

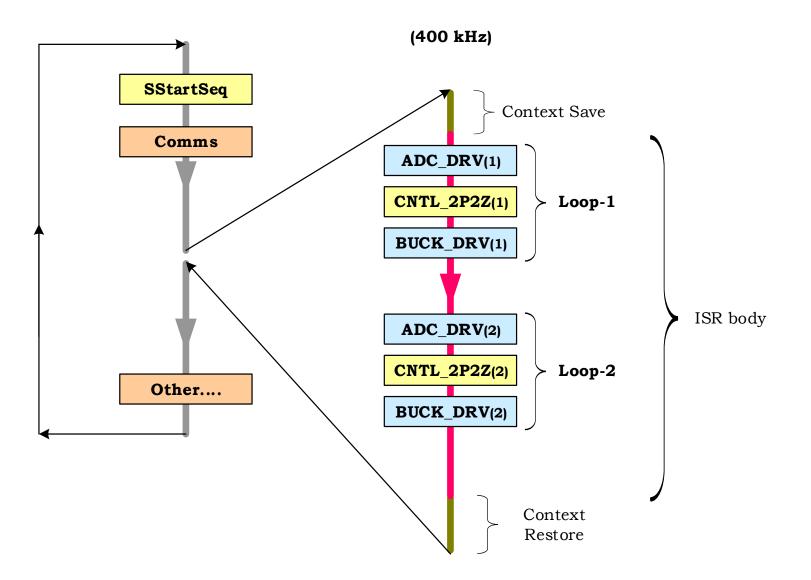

### Software Block Execution

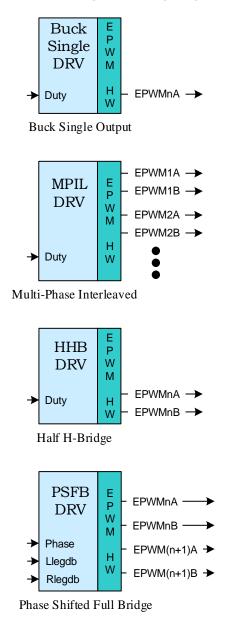

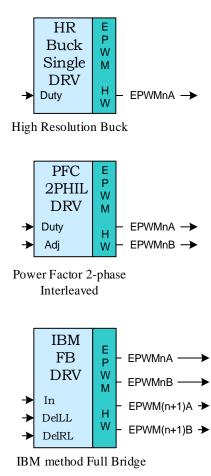

### Driving the Power Stage with PWM Waveforms

- Open-Loop System Block Diagram

- Generating PWM using the ePWM Module

- Power Stage Topologies and Software Library Support

## Simple Open-Loop Diagram

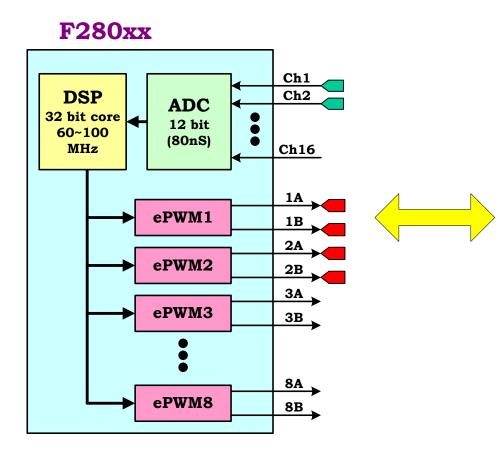

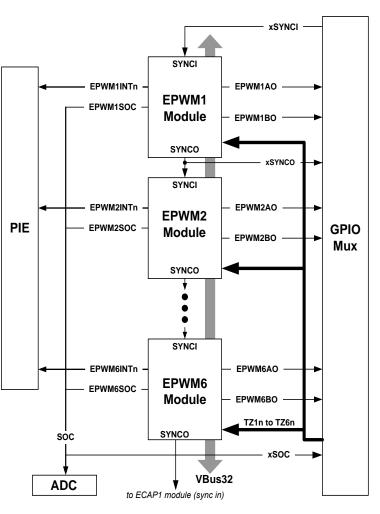

### Scaleable PWM Peripherals

Resources allocated on a per channel basis Each channel (module) supports 2 independent PWM outputs (A&B) □ # Channels easily scaleable – software reuse □ Time-base synch feature for all channels 6 modules (12 PWM outputs) on F2808 □ Key features: □Phase & edge control □New counting modes Independent deadband □ Flexible trip-zones □High frequency chopper mode

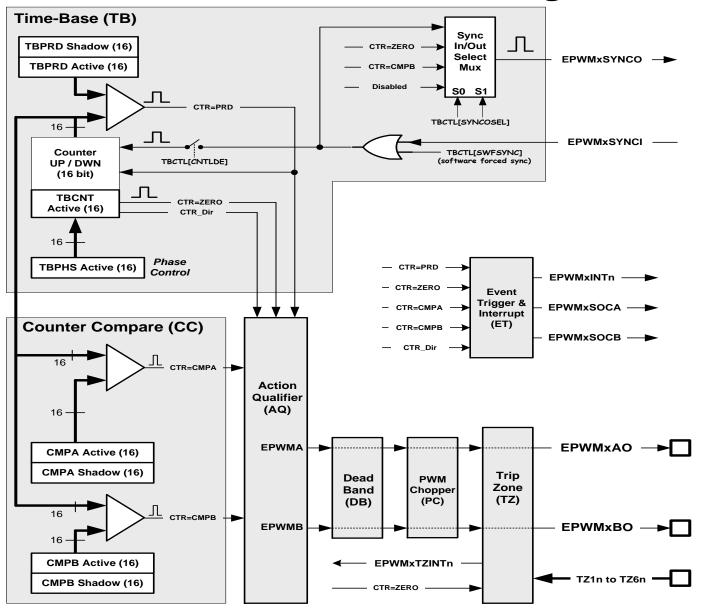

### ePWM Module Block Diagram

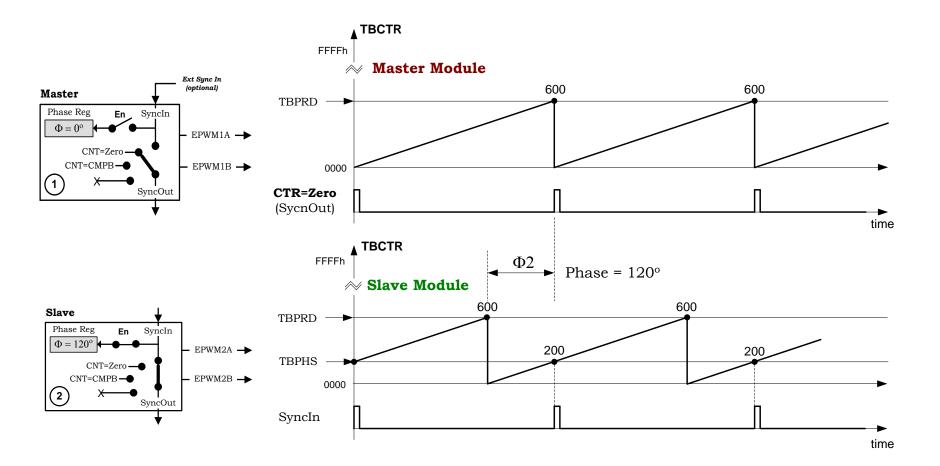

### Module Sync and Phase Control

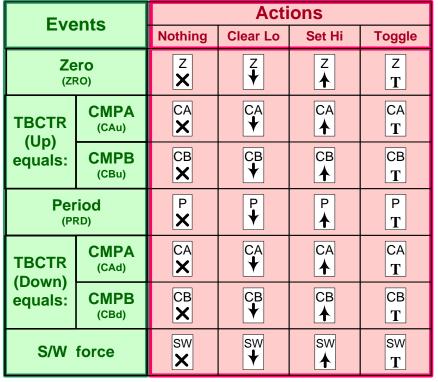

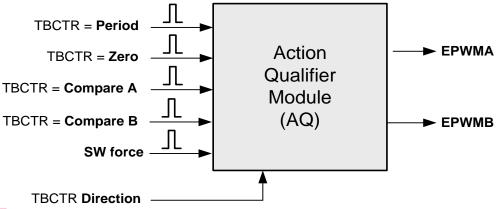

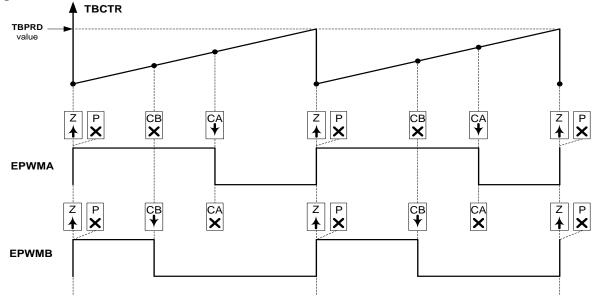

### Action Qualifier Module (AQ)

#### Key Features

- □ Multi event driven waveform generator

- □ Events drive outputs A and B independently.

- □ Full control on waveform polarity

- □ Full transparency on waveform construction

- □ S/W forcing events supported

- □ All events can generate interrupts & ADC SOC

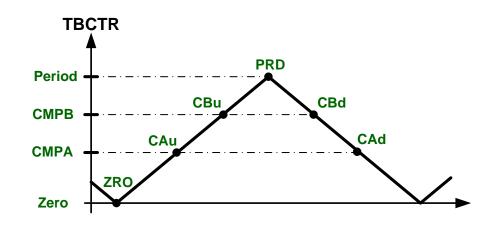

### Simple Waveform Construction

### Fault Management Support

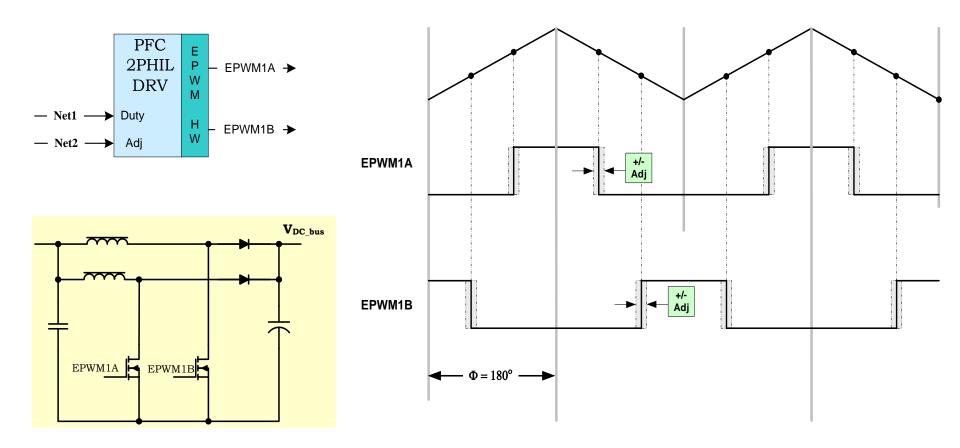

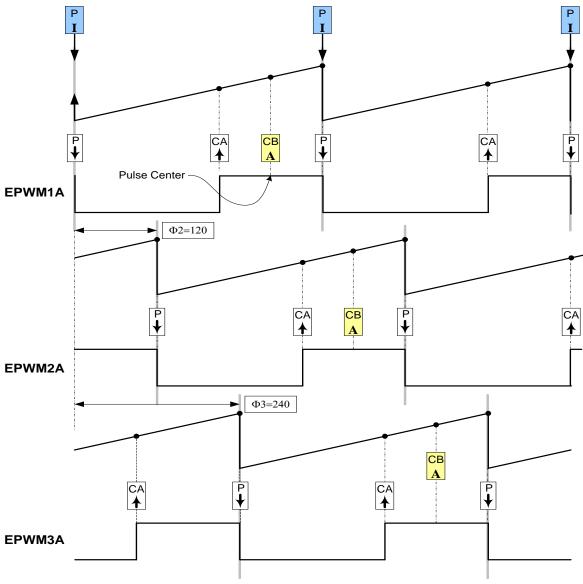

### Multi-Phase Interleaved (MPI)

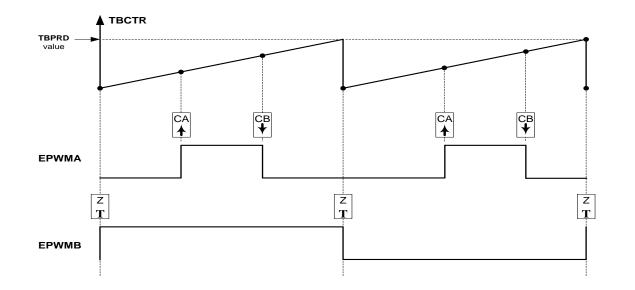

### Switching Requirements – MPI

- Asymmetrical PWM case

- Complementary output generated by dead-band unit

- CMPB triggers ADC SOC

#### INIT-time

- Period (1,2,3)

- CAu Action (1,2,3)

- PRD Action (1,2,3)

- Phase (2,3)

- PRD Interrupt (1)

- CBu ADC SOC (1,2,3)

- Dead-band

### RUN-time

- CMPA (1,2,3)

- CMPB (1,2,3)

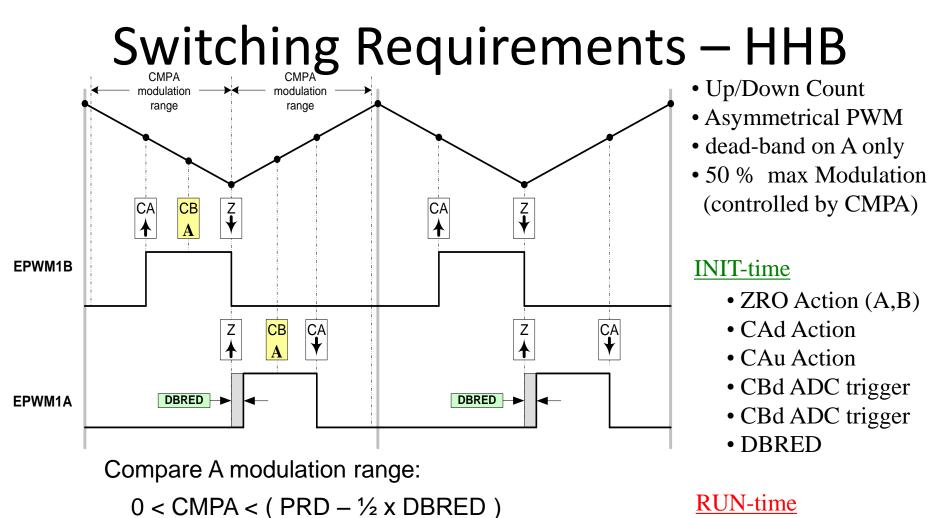

### Half H-Bridge (HHB)

- CMPA

- CMPB (optional)

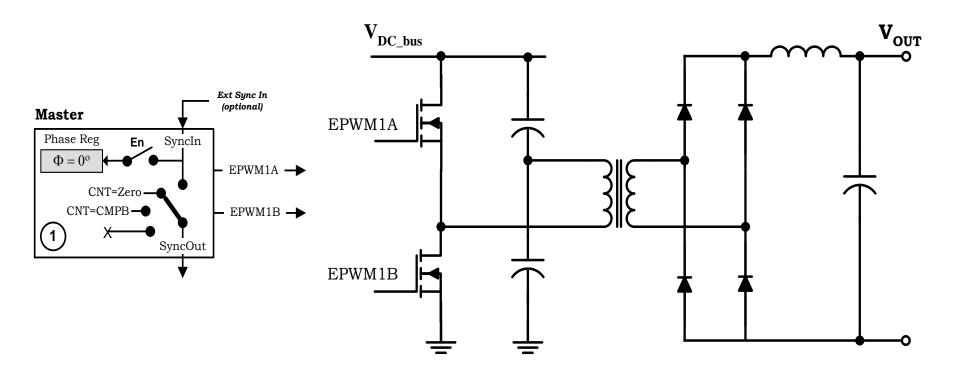

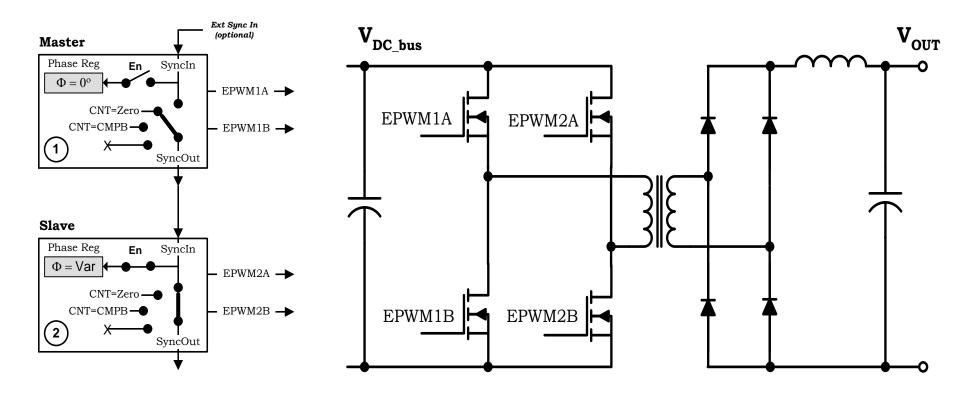

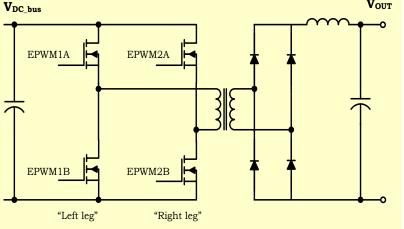

## Phase Shifted Full Bridge (PSFB)

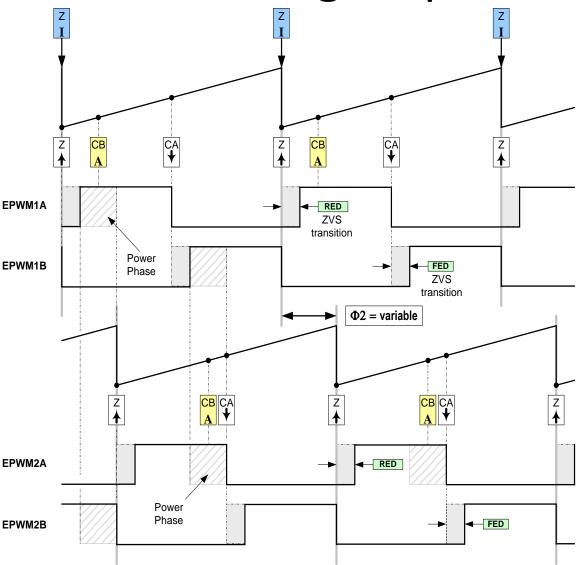

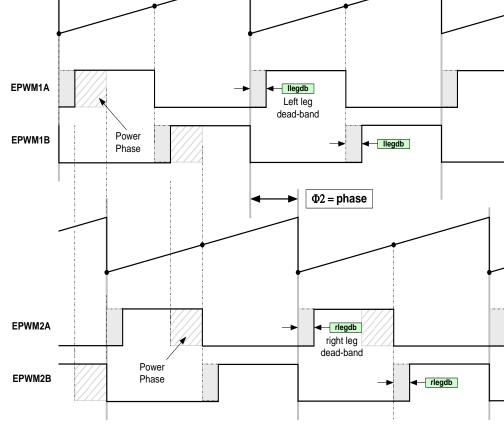

### Switching Requirements – PSFB

- Asymmetrical PWM

- Using dead-band module

- Phase  $(\Phi)$  is the control variable

- Duty fixed at ~ 50%

- RED / FED control ZVS trans. i.e. via resonance

- CMPB can trigger ADC SOC

#### INIT-time

- Period (1,2)

- CMPA (1,2) ~ 50%

- CAu action (1,2)

- ZRO action (1,2)

- CBu trigger for ADC SOC

### RUN-time

- Phase (2) every cycle

- FED / RED (1,2) slow loop

#### Software Driver Module – PSFB 50% duty **PSFB** Е EPWM1A -> DRV Ρ W EPWM1B -> Μ - Net1 --> phase EPWM1A llegdb EPWM2A -Left leg Н dead-band — Net2 —→ llegdb W EPWM2B -> Power EPWM1B - Net3 - rlegdb Ilegdb Phase $\Phi 2 = phase$ VOUT

### Software Driver Module – PFC2PHIL